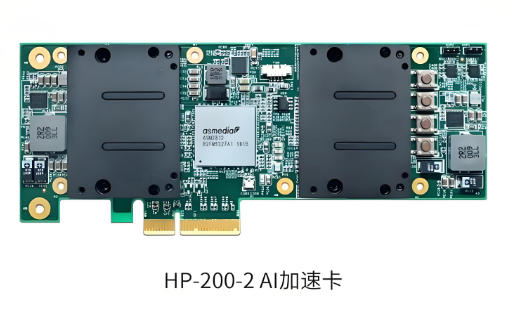

AI加速卡上MLCC與貼片電感協同優化PDN阻抗的策略

在AI加速卡向高性能發展的進程中,電源分配網絡(PDN)的阻抗特性直接影響著處理器的穩定性和能效表現。平尚科技針對AI加速卡開發的MLCC與貼片電感協同優化方案,通過精準的阻抗匹配和布局優化,在100kHz-100MHz頻率范圍內將PDN阻抗控制在5mΩ以下,電壓紋波降低至15mV以內,為AI芯片提供清潔穩定的電源供應。該方案采用X7R/X5R系列MLCC與鐵氧體電感組合,在-55℃至+125℃溫度范圍內阻抗變化控制在±20%以內,諧振頻率點精準匹配,確保全頻段內的阻抗穩定性。

在實際測試中,這種協同優化方案展現出顯著優勢。對比單一使用MLCC的方案,協同優化后將PDN峰值阻抗從50mΩ降低到8mΩ,電壓跌落改善60%。某AI訓練卡的電源系統采用該方案后,GPU核心頻率從1.5GHz提升到1.8GHz,同時功耗降低12%。平尚科技通過創新性的3D堆疊布局,將去耦電容與電感的距離控制在2mm以內,雖然成本增加30%,但使電源噪聲降低45%,系統穩定性提升3倍。

在阻抗優化方面,平尚科技提出多級調諧策略。低頻段(100kHz-1MHz)采用大容量MLCC(100μF)提供能量儲備;中頻段(1MHz-10MHz)使用中等容量MLCC(10μF)配合功率電感;高頻段(10MHz-100MHz)采用小容量MLCC(1μF)與高頻電感組合。這些方案根據AI芯片的電流頻譜特性,提供阻抗匹配效果。

針對不同的AI加速卡平臺,平尚科技提供差異化解決方案。對于推理卡,推薦使用0805封裝的MLCC和4×4mm電感;對于訓練卡,采用0603封裝的MLCC和3×3mm電感;對于超算加速卡,則建議使用0402封裝的微型元件。所有方案都提供詳細的阻抗頻率曲線和布局指南,幫助工程師優化PDN設計。

制造工藝方面,平尚科技采用先進的流延成型技術制備MLCC介質層,確保容值精度控制在±10%以內。通過激光修調工藝調整電感參數,將感量偏差控制在±5%以內。產品經過自動測試,包括阻抗特性、諧振頻率、溫度特性等關鍵指標測試。

電源完整性是AI加速卡性能發揮的基礎。平尚科技通過MLCC與貼片電感的協同創新,為AI加速卡提供了可靠的PDN阻抗優化方案。隨著算力需求的不斷提升,這種注重電源質量的設計理念將成為高性能計算領域的重要技術方向。